arcgis

django

centos

cloud alibaba

题解

labview

node

simulink

globalmapper

应届生就业

springboot

光源

求职招聘

reactjs

自由工作

堆排序

cisp题库

重定位

plugin

因果AI

SRIO

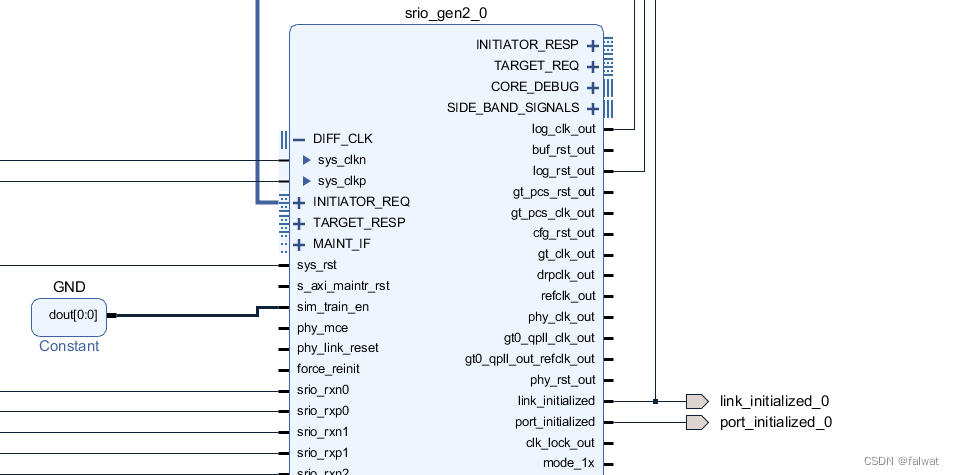

2024/4/22 17:55:24SRIO--IP讲解及环回测试

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、IP例化文件二、SRIO环回工程搭建三、板级验证3.1 本实验的板级验证环节,主要验证以下几个目标:3.2 系统所需硬件3.3 ILA波形前言

本章将为大家介绍 “Serial RapidIO Gen2 ”IP 的使用以…

RapidIO协议(1)

RapidIO协议 1.概述 1.1介绍 RapidIO是基于包交换互联协议,主要作为系统内部接口使用,如:芯片间、板间的通讯,速度能在GB/S数量级。如连接处理器、内存、内存映射的I/O设备。这些设备可能是网…

RapidIO协议(2)

2.RapidIO互连协议Part I:输入/输出逻辑协议 2.1系统模型 这一章介绍RapidIO系统可能的设备单元。 2.1.1处理单元模型 图1-1描述了可能的基于RapidIO的计算机系统,处理元素是一个计算机设备,比如&#x…

Xilinx平台SRIO介绍(四)SRIO IP核配置

干货来了,SRIO搬砖全靠它!! 汇总篇:

Xilinx平台SRIO介绍(汇总篇) 目录

前言

一、第一页配置(Basic)

二、第二页配置(logic layer)

三、第三页配置&#…

Xilinx平台SRIO介绍(二)SRIO IP核基础知识

使用SRIO IP核必须掌握的基础知识!理解了这篇,剩下的只是代码罢了。 汇总篇:

Xilinx平台SRIO介绍(汇总篇) 目录

前言:SRIO 、RapidIO、GT 有什么关系?

一、SRIO IP核概述

1.1概述

1.2 SRIO…

Xilinx平台SRIO介绍(汇总篇)

用最简单直白的语言记录复杂的FPGA设计。

——FPGA大叔沃自己硕得 目录

前言

一、SRIO扫盲篇——RapidIO协议介绍

二、Xilinx平台SRIO - IP核基础知识

三、SRIO时钟与复位

四、SRIO IP核配置使用教程

五、示例工程Example Design介绍

六、SRIO收发测试

后记 前言

本文…

Xilinx平台SRIO介绍(六)SRIO收发测试

SRIO简单应用指南。 汇总篇:

Xilinx平台SRIO介绍(汇总篇) 目录

前言

一、HELLO格式

二、收发测试

后记 前言 Example Design一堆.v文件看着很不爽怎么办,删掉删掉! 使用我们自己的发送/接收模块,两个字…

Xilinx平台SRIO介绍(五)示例工程Example Design介绍

理解IP的使用,少不了Example Design的学习。 汇总篇:

Xilinx平台SRIO介绍(汇总篇)

目录: 一、示例工程架构组成

到了这一步,默认你已经生成IP并打开示例工程了。

首先,我们展开示例工程目录…

Xilinx平台SRIO介绍(三)时钟与复位

时钟,又见时钟。顺便带上复位。 汇总篇:

Xilinx平台SRIO介绍(汇总篇) 目录

一、IP核时钟

二、时钟参考设计

三、复位

四、时钟与复位小结 一、IP核时钟

PHY(物理层)在两个时钟域上运行:

phy_clk&…

Tsi721信号及处理

Tsi721信号及处理 1. PCIe信号 名称 类型 描述 PCTP[3:0] PCTN[3:0] PCIE_O PCIe端口的差分发送数据 PCRP[3:0] PCRN[3:0] PCIE_I PCIe端口的差分接收数据 PCCLKP PCCLKN DIFF_I PCIe参考时钟输入 当在PCIe…

Xilinx平台SRIO介绍(一)RapidIO协议介绍

菜鸟到老鸟:会用工具;

老鸟到大佬:深入理解原理。

——FPGA大叔沃自己硕得 目录 一、RapidIO背景介绍

二、RapidIO协议概述

2.1 包与控制符号

2.2 包格式

2.3 事务格式与类型

2.4 消息传递

2.5 全局共享存储器

2.6 流量控制

2.7 串…

SRIO—IP讲解及说明

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 前言一、SRIO IP 概述1.1 逻辑层1.1.1 I/O 端口(I/O Port)1.1.2 消息端口(Messaing Port)1.1.3 用户自定义端口(User-Defined Port)1.1.4 维护端口(Maintenance Port)1.2 缓冲层1.3 物理层…

创龙TL6678F开发板: 实现FPGA与DSP之间 SRIO(3.125Gbps, 4x)通信

创龙TL6678F开发板官方Demo:SRIO_AD9613 实现了FPGA和DSP之间的SRIO通信, SRIO的速率为5Gbps. 在FPGA端, srio_gen_2 模块的参考时钟为 125MHz. 而Demo: udp_10g_echo 实现了10G以太网通信, ten_gig_eth_pcs_pma模块的参考时钟为156.25 MHz. 两者共用一个 cdcm61002, 且两个参考…